Welcome to EuroSOI-ULIS 2025!

On behalf of the Steering and Organizational Committee, we are honored to invite you to 11th Joint EuroSOI Workshop and International Conference on Ultimate Integration on Silicon (EuroSOI-ULIS 2025), which will be held on May 14-16, 2025, in Warsaw, Poland!

The Joint EuroSOI-ULIS Conference has been an annual event since 2013. The past conferences in this series were organized in Athens, Greece (2017); Granada, Spain (2018); Grenoble, France (2019); Caen, France (2020/virtual and 2021); Udine, Italy (2022); Tarragona, Spain (2023); and Athens, Greece (2024). The organizer of next year’s EuroSOI-ULIS conference edition is the Warsaw University of Technology, the best technical University in Poland.

We are happy to announce that the Conference will be held under the honorary patronage of the Rector of the Warsaw University of Technology!

This Conference aims to gather all scientists and engineers working in the field of SOI technology and nanoscale devices in More-Moore, More-Than-Moore, and Beyond CMOS era in an interactive and pleasant forum. One of the key objectives of the Conference is to promote collaboration and partnership between different academia, research, and industry players in the field.

We cordially invite all students and researchers working in the areas related to the Conference’s topics to submit their abstracts, attend the Conference, meet their colleagues, and enjoy the vibrant atmosphere of the Conference, and the city of Warsaw as well.

We count on your presence. See you soon in Warsaw!

Robert Mroczyński, PhD DSc

General Chair

CALL FOR PAPERS

On behalf of the Steering and Organizational Committee, we are honored to invite you to 11th Joint EuroSOI Workshop and International Conference on Ultimate Integration on Silicon (EuroSOI-ULIS 2025), which will be held on May 14-16, 2025, in Warsaw, Poland! The Conference aims to gather all scientists and engineers working in the field of SOI technology and nanoscale devices in More-Moore, More-Than-Moore, and Beyond CMOS era.

High-quality contributions in the following areas are solicited:

- Advanced SOI materials and structures, innovative SOI-like devices.

- Alternative transistor architectures (FDSOI, Nanowire, Nanosheet, FinFET, MuGFET, vertical MOSFET, FeFET and TFET, MEMS/NEMS, Beyond-CMOS).

- New channel materials for CMOS (strained Si/SOI, SiGe, GeOI, III-V and high mobility materials on insulator, carbon nanotubes, graphene, and other 2D materials).

- Nanometer scale devices: technology, characterization techniques, and evaluation metrics for high performance, low power, low standby power, high frequency, and memory applications.

- New functionalities and innovative devices in the More-than-Moore domain: nanoelectronic sensors, biosensor devices, memristors, neuromorphic computing devices, quantum computing devices, energy harvesting devices, RF devices, imagers, integrated photonics (on SOI), etc.

- Transport phenomena, compact modeling, device simulation, front- and back-end process simulation.

- CMOS scaling perspectives; device/circuit level performance evaluation; switches and memory scaling; three-dimensional integration of devices and circuits, heterogeneous integration.

- Advanced test structures, characterization techniques, parameter extraction, reliability, and variability assessment techniques for new materials and novel devices.

The “Androula Nassiopoulou Best Paper Award” will be attributed by the SINANO Institute, while the ELSEVIER will attribute the “Best Poster Award”.

In addition, an ICOS Workshop will take place on May 12th – 13th 2025 at the CEZAMAT WUT (free registration).

During the ICOS Workshop, you will be able to discover the FAMES Pilot line. FAMES allows you to explore and test advanced FD-SOI technologies, embedded non-volatile memories, 3D integration options, RF components, and smart power management integrated circuit solutions.

The wide array of FAMES technologies is available through open calls for projects, spontaneous User Requests, education, training, PDKs, specific fabrication modules, and processing steps. Anyone interested is welcome to register here.

Important dates

abstract submission deadline

January 31, 2025

February 17, 2025

February 24, 2025

Notification of acceptance

February 22, 2025

March 10, 2025

March 14, 2025

early bird registration

by April 17, 2025

Deadline for the 4-page paper submission to the Special Issue of Solid-State Electronics

May 5, 2025

May 23, 2025

(in the picture) Maria Salomea Skłodowska-Curie, the first woman to win a Nobel Prize

Abstracts

You can send your abstracts through our online administration system (as of Feb 24, 2025, submission is closed). Submissions will be open starting December 9th, 2024. Original 2-page abstracts with illustrations will be accepted for review in pdf format. Papers submitted for review should clearly state:

- the purpose of the work,

- how and to what extent it advances the state-of-the-art,

- specific new results and their impact.

The degree to which the paper deals with these issues will affect the paper selection. The most frequent cause of rejection of submitted papers is a lack of new results. Only work not published at the time of the Conference will be considered. The Scientific Committee considers submitting a paper for review and subsequent acceptance as an agreement that the work will not be placed in the public domain before the Conference.

The Book of Abstracts will be printed in the B5 format size; thus, please do NOT change the font size embedded in the template (it will enable the proper down-scaling of the submitted document). You may print your figures down-scaled to 80% of the original size submitted in the document to ensure they will be legible in the color B5 hard copy format. The abstract template is available here.

The Scientific Committee will review original 2-page abstracts with illustrations. The accepted contributions will be published as a Book of Abstracts with ISBN. Selected papers will be published in 4-page letters in the Special Issue of the Solid-State Electronics journal (ELSEVIER).

Special Issue of Solid-State Electronics

More information about the Special Issue can be found here. Authors of 4-page papers are encouraged to use the submission website for Solid-State Electronics at https://www.editorialmanager.com/sse/default.aspx .

The deadline for the 4-page paper submission to the Special Issue of Solid-State Electronics is May 5th, 2025. To ensure that all manuscripts are correctly identified for inclusion in the special issue, it is important that authors select VSI: EuroSOI-ULIS 2025.

Guidelines for accepted contributions

Posters should be printed at maximal A0 size. (84 x 118 cm). To all interested participants, we will provide a poster printing service on-site (free of charge). Panels will be available all the time during the Conference.

The Poster Session will be preceded by a Poster short presentations session. Please use our template. The template for short presentations can be downloaded from here (1 minute: 1 title slide + up to 2 slides with your content). Short presentation files should be sent in PDF format to the conference email address (subject line: short presentation) by May 12th. The short presentations are mandatory for Best Poster Award contestants. Poster presenters not taking part in the competition may participate in the session at their discretion.

The duration of a contributed talk will be 20 minutes, including the time for addressing questions from the audience. For invited talks, the duration is 35 minutes + 5 min for questions.

A computer will be provided for presentations; presentation files can be either emailed to office@eurosoi-ulis2025.pl before the conference or transferred from USB drive at least one session before the ultimate presentation. In any case, please be present in the room during the coffee break before the start of your session and introduce yourself to the session chair.

Visa

A valid passport is required for everyone wishing to enter Poland except for European citizens for whom a valid Identity Card is enough. The visa requirement depends on the home Country of citizenship. To find out whether you need a visa or not, please visit the website of the Ministry of Foreign Affairs of the Republic of Poland. More info can also be found here.

If you need a personal letter of invitation to attend the Conference, please contact the secretariat.

Invited speakers

Claire FENOUILLET-BERANGER joined CEA-Leti, Grenoble, in 1998, where she carried out her PhD thesis on the integration and characterization of SOI devices. From 2001 to 2013, she worked on FD-SOI technology platform development and characterization as a CEA-Leti assignee in the advanced R&D STMicroelectronics center, Crolles, France. From 2013 to 2020, she was the project leader in developing low-temperature MOSFETs for 3D sequential integration. From January 2020 to January 2022, she was the LETI SiC pilot line project manager in the frame of the joint development program between SOITEC & AMAT. She is the author and co-author of over 200 publications in major conferences and journals and of more than 40 patents. She was the co-recipient of the Grand Prix du Général Ferrié in 2012 for her work on FD-SOI. She is in charge of CMOS patent portfolio. Since 2022, she has been director of research, CEA Fellow expert, and co-project manager of the FD-SOI next-generation node integration at CEA-Leti.

Xinran WANG received B.S. in physics from Nanjing University in 2004 and Ph.D. in physics from Stanford University in 2010. Between 2010 and 2011, he was a postdoctoral researcher at Stanford University and then at the University of Illinois at Urbana-Champaign. He then joined the faculty of Nanjing University, where he is currently a full professor and Dean of the School of Integrated Circuits. His research interest includes 2D semiconductor materials growth, device technology, and integrated circuits. He has already published over 200 papers in peer-reviewed journals and conferences with more than 39,000 citations. He is an IEEE Fellow and has been recognized with several awards, including Xplorer Prize, Clarivate Highly Cited Researcher, Huang Kun Prize in Solid-state Physics and Semiconductor Physics, National Natural Science Award, and Chinese Youth Medal.

Professor Mikael ÖSTLING received his MSc and the PhD degrees from Uppsala University, Sweden. He holds a position as professor in solid state electronics at KTH, Royal Institute of Technology in Stockholm, Sweden. He was the deputy president of KTH 2017-2022. He previously held the position as dean of the School of Information and Communication Technology, KTH, and head of department. Mikael was a senior visiting Fulbright Scholar at Stanford University, and a visiting professor with the University of Florida, Gainesville. Mikael was an editor of the IEEE Electron Device Letters and EiC of IEEE J-EDS. He is a Life Fellow of the IEEE and Fellow of the Electrochemical Society.

Minsoo YOO received his Ph.D. in Materials Science and Engineering from Pohang University of Science and Technology (POSTECH), South Korea, in 2003. With over 20 years of experience in the semiconductor industry, he specializes in process technology, device design, and transistor reliability. Since joining SK hynix in 2003, he has played a key role in advancing DRAM transistor performance and reliability. Currently serving as Vice President and Research Fellow, he oversees transistor performance and reliability across all DRAM products. He holds more than 50 patents and has authored 26 publications in the field.

Pricing

Please follow the one contribution - one registration policy

Student

Full participant

Early (by April 17)

Late

Fee includes:

entrance to all sessions, conference materials, coffee breaks, lunches, welcome reception, and gala dinner

Accompanying person

welcome reception and conference gala dinner

Welcome to Warsaw

Warsaw is the capital of Poland and its biggest city. The city was a witness of wars and the Warsaw Uprising during the II World War (in 1944), during which it was almost wholly destroyed. Rebuilt after the war, it has kept its historical atmosphere in the Old Town. Nowadays, Warsaw is Poland’s business center with headquarters of many international companies. The city is divided into 18 districts.

Each city has a place that is its showcase and a must-see on any trip. In Warsaw, it’s the Old Town, entered on the UNESCO World Heritage List – it’s where the city’s heart has been beating for centuries. However, when you cross the Vistula River and look at the Old Town from a distance, you are struck by how unusual the city’s panorama is – skyscrapers rise above the red roofs of the Old Town. Historical buildings blend in harmoniously with modern architecture, and the city surprises us by revealing its second face.

Conference venue

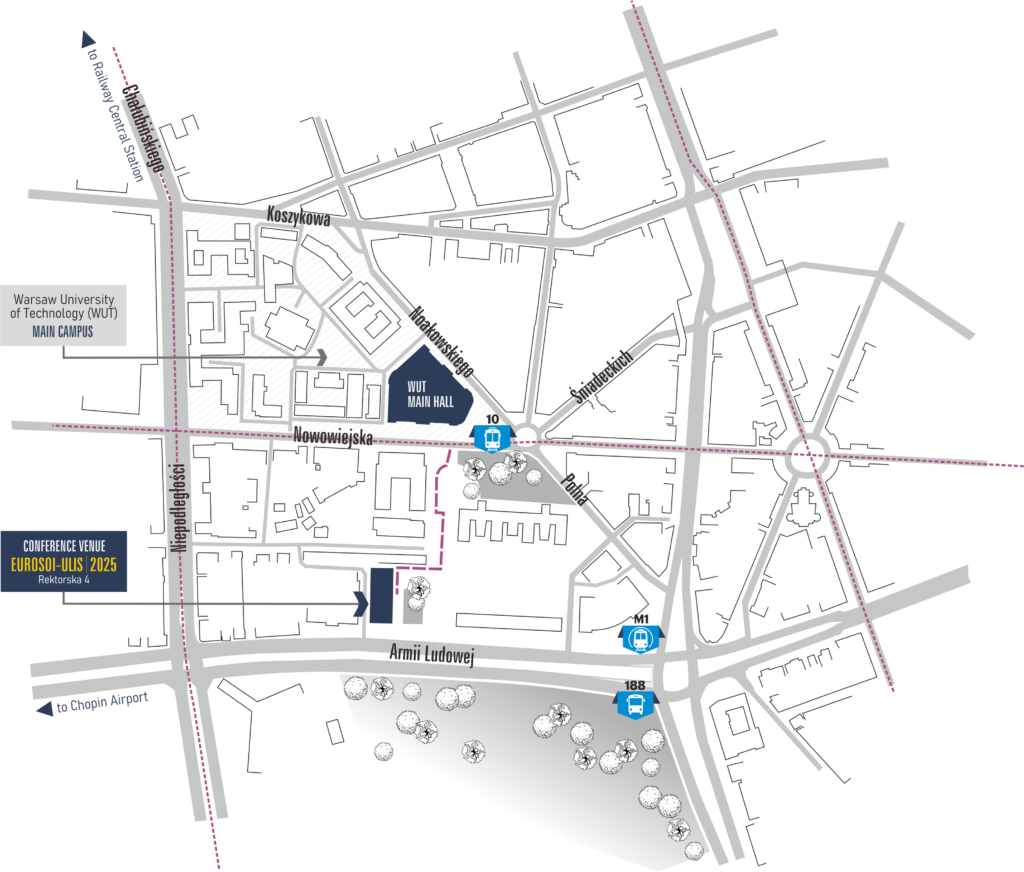

WUT (Warsaw University of Technology / Politechnika Warszawska) Main Campus is located in the most central district of Warsaw called “Śródmieście”. It can be reached from the Chopin Airport by bus within 26 minutes. The Conference Venue is beside the Main Campus at 4 Rektorska Str.

Social program

Welcome Cocktail

When: 14 May at 7:30 p.m.

Where: W Orbicie Słońca (Bistro & Bar)

Address: Marszałkowska 45/49, 00-401 Warszawa

Gala Dinner

When: 15 May, departure from the conf. venue at 7:00 p.m.

We warmly invite you to experience the charm of Warsaw’s Old Town. Coaches will depart from the Conference Venue, taking you on a guided tour to the historic Old Town district. From Castle Square, a brief stroll will lead you to the picturesque Old Town Market Place, where we will welcome you to the Bazyliszek Restaurant (Rynek Starego Miasta 1/3) for the Gala Dinner. The dinner will begin at approx. 8:00 p.m.

After the evening’s festivities, return transportation to the Conference Venue will be provided.

Airports

Two airports serve the Warsaw agglomeration (see the map above). More convenient is to use the Chopin Airport, located in the urban area of Warsaw. The other one is the Modlin Airport, located about 45 kilometers from the city center/conference venue.

✈ The Chopin Airport (WAW) ✈

The airport Taxi rank at the Chopin Airport is located outside of Terminal 2 in front of the airport building exit at the Arrivals level. You will find official taxis waiting to pick up the customers there. The cost of the travel to the conference venue (@ daytime & weekdays) is about 12 EUR (distance: 7 kilometers).

The conference venue may also be reached by bus: take bus 188 in front of the Airport Exit gates (timetable) and get off at the METRO POLITECHNIKA 01 stop. When you get off the bus, you need to walk about 900 m to REKTORSKA 4. Bus tickets are sold in machines on the bus.

By bus line 175 you may get from the airport to the city center. Another way to reach the city center and the Railway Central Station (Warszawa Centralna) is to take a train directly from the airport (look here for more information). When you leave the baggage claims area, you must follow colored lines on the floor.

✈ The Modlin Airport (WMI) ✈

CONTBUS and FLIXBUS offer direct bus connections from Warsaw Modlin Airport to Warsaw. The journey to the Warsaw City Centre takes about 1 hour. There are two options:

Direct routes to the City Center (operated by Flixbus and Contbus), the arrival is near the Railway Central Station (Dworzec Centralny). From there, you may use a tram to get to the conference venue (see the Railway section for details).

Routes (Flixbus) to the Metro Młociny Underground Station: the final terminal or a stop-over for routes to (Warszawa, Dworzec Autobusowy Zachodni) and (Warszawa, Metro Stadion Narodowy). Take the M1 Underground line from “Młociny” to “Politechnika” Station. Take the exit to the right at the head of the train, and you need to walk about 900 m to REKTORSKA 4.

Alternatively, Taxi Modlin offers direct taxi transfers to the City of Warsaw.

Taxis

We advise you to use official companies only (see below).

- City Taxi +48 22 848 88 88

- Wawa Taxi +48 22 333 44 44

- Ele Taxi +48 22 811 11 11

- MPT Taxi +48 22 19191

- Sawa Taxi +48 22 644 44 44

- Eco Car +48 123456789

There is also Uber, Bolt and FreeNow. Receipts are available.

Railway

To reach WUT from Railway Central Station (Warszawa Centralna / Dworzec Centralny), take the tram line 10 or 11 on the side of the station building (tram stop: Dworzec Centralny 09) and get off at the Pl. POLITECHNIKI 01 stop (travel time: 5 minutes). Tram tickets are sold in machines on the tram.

Accommodation

We recommend that participants use portals such as booking.com and Airbnb to look for short-term rentals in Warsaw.

Hampton by Hilton Warsaw City Centre

Address: Wspólna 72, 00-687 Warszawa

The hotel offers a 12% discount for the period 13-16.05.2025. Write directly to wawct_hampton@hilton.com, referring to “EuroSOI-ULIS”. Please be aware that this is a non-refundable offer.

MDM Hotel Warsaw

Address: Pl. Konstytucji 1, 00-647 Warszawa

Please remember that the host university cannot offer any reimbursements in case of your hotel booking cancellation.

Basic travel information can be found here:

Committees

Steering Committee

Francis BALESTRA (CROMA, France)

Maryline BAWEDIN (CROMA, France)

Cor CLAEYS (KU-Leuven, Belgium)

Bogdan CRETU (ENSICAEN, France)

Sorin CRISTOLOVEANU (IMEP-LAHC, France)

Panagiotis DIMITRAKIS (DEMOKRITOS, Greece)

Francisco GAMIZ (University of Granada, Spain)

Elena GNANI (University of Bologna, Italy)

Benjamin INIGUEZ (Universitat Rovira i Virgili, Spain)

Joris LACORD (CEA-Leti, France)

Robert MROCZYŃSKI (Warsaw University of Technology, Poland)

Pierpaolo PALESTRI (University of Modena and Reggio Emilia, Italy)

Enrico SANGIORGI (University of Bologna, Italy)

Luca SELMI (University of Modena, Italy)

Viktor SVERDLOV (TU Wien, Austria)

Organizing Committee

Robert MROCZYŃSKI – General Chair (Warsaw University of Technology, Poland)

Marcin KIELISZCZYK (Warsaw University of Technology, Poland)

Andrzej MAZURAK (Warsaw University of Technology, Poland)

Jakub WALCZAK (Warsaw University of Technology, Poland)

Piotr WIŚNIEWSKI (CEZAMAT, Warsaw University of Technology, Poland)

& Hanna SATER

Technical Program Committee

Francis BALESTRA (CROMA, France)

Maryline BAWEDIN (CROMA, France)

Bogdan CRETU (ENSICAEN, France)

Sorin CRISTOLOVEANU (IMEP-LAHC, France)

Luca DONETTI (University of Granada, Spain)

Panagiotis DIMITRAKIS (DEMOKRITOS, Greece)

Francisco GAMIZ (University of Granada, Spain)

Vihar GEORGIEV (University of Glasgow, UK)

Gerard GHIBAUDO (IMEP Minatec, France)

Farzan GITY (Tyndall Institute Cork, Ireland)

Paschalis GKOUPIDENIS (Max Planck Institute, Germany)

Elena GNANI (University of Bologna, Italy)

Irina IONICA (INP Grenoble, France)

Valeriya KILCHYTSKA (Catholic University of Louvain-la-Neuve, Belgium)

Sungjun KIM (Dongguk University, Korea)

Joris LACORD (CEA-Leti, France)

Carlos MARQUEZ (CITIC, University of Granada, Spain)

Joao Antonio MARTINO (University of Sao Paulo, Brazil)

Robert MROCZYŃSKI (Warsaw University of Technology, Poland)

Pierpaolo PALESTRI (University of Modena and Reggio Emilia, Italy)

Luca PIRRO (Global Foundries, Germany)

Quentin RAFHAY (IMEP Minatec, France)

Jean-Pierre RASKIN (Catholic University of Louvain-la-Neuve, Belgium)

Carlos SAMPEDRO (University of Granada, Spain)

Enrico SANGIORGI (University of Bologna, Italy)

Viktor SVERDLOV (TU Wien, Austria)

Christoforos THEODOROU (CROMA, France)

Alexander ZASLAVSKY (Brown University, USA)

Cezar ZOTA (IBM Zurich, Switzerland)